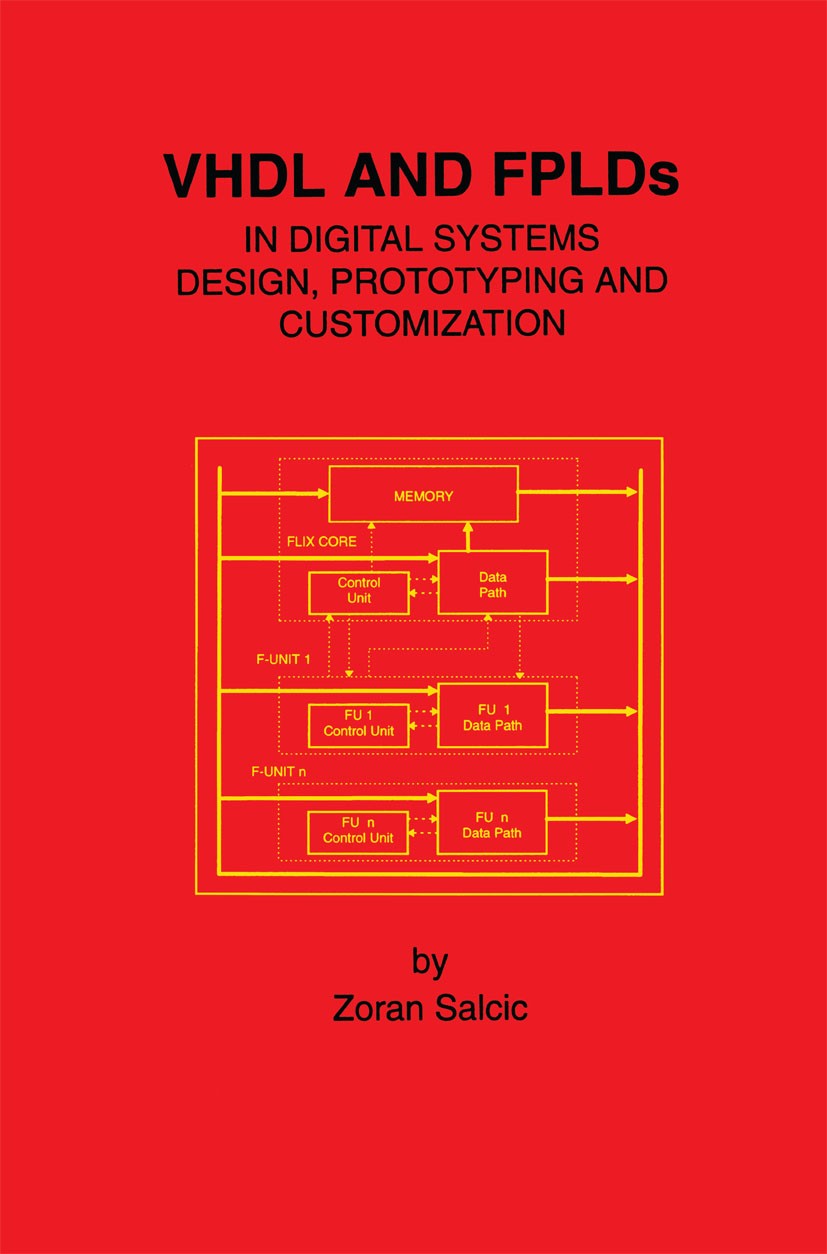

| 書(shū)目名稱 | VHDL and FPLDs in Digital Systems Design, Prototyping and Customization | | 編輯 | Zoran Salcic | | 視頻video | http://file.papertrans.cn/981/980057/980057.mp4 | | 圖書(shū)封面 |  | | 描述 | This book represents an attempt to treat three aspects of digital systems, design, prototyping and customization, in an integrated manner using two major technologies: VHSIC Hardware Description Language (VHDL) as a modeling and specification tool, and Field-Programmable Logic Devices (FPLDs) as an implementation technology. They together make a very powerful combination for complex digital systems rapid design and prototyping as the important steps towards manufacturing, or, in the case of feasible quantities, they also provide fast system manufacturing. Combining these two technologies makes possible implementation of very complex digital systems at the desk. VHDL has become a standard tool to capture features of digital systems in a form of behavioral, dataflow or structural models providing a high degree of flexibility. When augmented by a good simulator, VHDL enables extensive verification of features of the system under design, reducing uncertainties at the latter phases of design process. As such, it becomes an unavoidable modeling tool to model digital systems at various levels of abstraction. | | 出版日期 | Book 1998 | | 關(guān)鍵詞 | Hardware; Hardwarebeschreibungssprache; Programmable Logic; Software; VHDL; architecture; computer; digital | | 版次 | 1 | | doi | https://doi.org/10.1007/978-1-4615-5827-9 | | isbn_softcover | 978-1-4613-7671-2 | | isbn_ebook | 978-1-4615-5827-9 | | copyright | Springer Science+Business Media New York 1998 |

The information of publication is updating

書(shū)目名稱VHDL and FPLDs in Digital Systems Design, Prototyping and Customization影響因子(影響力)

書(shū)目名稱VHDL and FPLDs in Digital Systems Design, Prototyping and Customization影響因子(影響力)學(xué)科排名

書(shū)目名稱VHDL and FPLDs in Digital Systems Design, Prototyping and Customization網(wǎng)絡(luò)公開(kāi)度

書(shū)目名稱VHDL and FPLDs in Digital Systems Design, Prototyping and Customization網(wǎng)絡(luò)公開(kāi)度學(xué)科排名

書(shū)目名稱VHDL and FPLDs in Digital Systems Design, Prototyping and Customization被引頻次

書(shū)目名稱VHDL and FPLDs in Digital Systems Design, Prototyping and Customization被引頻次學(xué)科排名

書(shū)目名稱VHDL and FPLDs in Digital Systems Design, Prototyping and Customization年度引用

書(shū)目名稱VHDL and FPLDs in Digital Systems Design, Prototyping and Customization年度引用學(xué)科排名

書(shū)目名稱VHDL and FPLDs in Digital Systems Design, Prototyping and Customization讀者反饋

書(shū)目名稱VHDL and FPLDs in Digital Systems Design, Prototyping and Customization讀者反饋學(xué)科排名

|

|

|

|Archiver|手機(jī)版|小黑屋|

派博傳思國(guó)際

( 京公網(wǎng)安備110108008328)

GMT+8, 2025-10-9 15:47

|Archiver|手機(jī)版|小黑屋|

派博傳思國(guó)際

( 京公網(wǎng)安備110108008328)

GMT+8, 2025-10-9 15:47